کیا آپ جانتے ہیں کہ ملٹی لیئر پی سی بی ڈیزائن کرتے وقت EMI کا مسئلہ کیسے حل کیا جائے؟

میں آپ کو بتاتا ہوں!

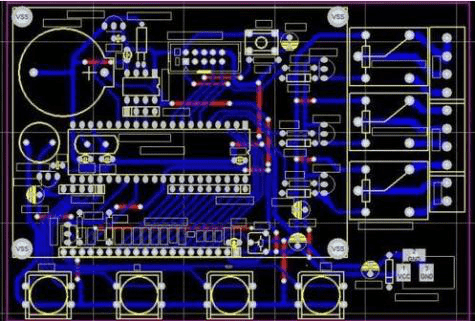

EMI کے مسائل کو حل کرنے کے بہت سے طریقے ہیں۔EMI دبانے کے جدید طریقوں میں شامل ہیں: EMI سپریشن کوٹنگ کا استعمال، مناسب EMI دبانے والے پرزوں کا انتخاب اور EMI سمولیشن ڈیزائن۔پی سی بی کی سب سے بنیادی ترتیب پر مبنی، یہ مقالہ EMI تابکاری کو کنٹرول کرنے میں PCB اسٹیک کے فنکشن اور PCB ڈیزائن کی مہارتوں پر بحث کرتا ہے۔

پاور بس

IC کے آؤٹ پٹ وولٹیج جمپ کو IC کے پاور پن کے قریب مناسب capacitance رکھ کر تیز کیا جا سکتا ہے۔تاہم، یہ مسئلہ کا خاتمہ نہیں ہے.کپیسیٹر کے محدود فریکوئنسی رسپانس کی وجہ سے، کپیسیٹر کے لیے مکمل فریکوئنسی بینڈ میں IC آؤٹ پٹ کو صاف طور پر چلانے کے لیے درکار ہارمونک پاور پیدا کرنا ناممکن ہے۔اس کے علاوہ، پاور بس پر بننے والا عارضی وولٹیج ڈیکپلنگ پاتھ کے انڈکٹنس کے دونوں سروں پر وولٹیج گرنے کا سبب بنے گا۔یہ عارضی وولٹیج اہم عام موڈ EMI مداخلت کے ذرائع ہیں۔ہم ان مسائل کو کیسے حل کر سکتے ہیں؟

ہمارے سرکٹ بورڈ پر IC کی صورت میں، IC کے ارد گرد موجود پاور لیئر کو ایک اچھا ہائی فریکوئنسی کپیسیٹر سمجھا جا سکتا ہے، جو صاف آؤٹ پٹ کے لیے ہائی فریکوئنسی توانائی فراہم کرنے والے مجرد کپیسیٹر سے لیک ہونے والی توانائی کو اکٹھا کر سکتا ہے۔اس کے علاوہ، اچھی پاور لیئر کا انڈکٹنس چھوٹا ہوتا ہے، اس لیے انڈکٹر کے ذریعے ترکیب شدہ عارضی سگنل بھی چھوٹا ہوتا ہے، اس طرح عام موڈ EMI کو کم کرتا ہے۔

بلاشبہ، پاور سپلائی لیئر اور IC پاور سپلائی پن کے درمیان کنکشن جتنا ممکن ہو چھوٹا ہونا چاہیے، کیونکہ ڈیجیٹل سگنل کا بڑھتا ہوا کنارہ تیز اور تیز ہوتا ہے۔بہتر ہے کہ اسے براہ راست پیڈ سے جوڑیں جہاں IC پاور پن واقع ہے، جس پر الگ سے بات کرنے کی ضرورت ہے۔

کامن موڈ EMI کو کنٹرول کرنے کے لیے، پاور لیئر کو ایک اچھی طرح سے ڈیزائن کیا گیا پاور لیئرز کا جوڑا ہونا چاہیے تاکہ ڈیکپل میں مدد ملے اور اس میں کافی حد تک کم انڈکٹنس ہو۔کچھ لوگ پوچھ سکتے ہیں، یہ کتنا اچھا ہے؟جواب پاور پرت، تہوں کے درمیان مواد، اور آپریٹنگ فریکوئنسی پر منحصر ہے (یعنی، IC عروج کے وقت کا ایک فنکشن)۔عام طور پر، پاور لیئرز کا فاصلہ 6mil ہے، اور انٹر لیئر FR4 میٹریل ہے، لہذا پاور لیئر کے فی مربع انچ کے مساوی گنجائش تقریباً 75pF ہے۔ظاہر ہے، پرت کا فاصلہ جتنا چھوٹا ہوگا، گنجائش اتنی ہی زیادہ ہوگی۔

100-300ps کے اضافے کے وقت کے ساتھ بہت سے آلات نہیں ہیں، لیکن IC کی موجودہ ترقی کی شرح کے مطابق، 100-300ps کی حد میں اضافے کے وقت والے آلات زیادہ تناسب پر قبضہ کریں گے۔100 سے 300 PS کے عروج کے اوقات والے سرکٹس کے لیے، 3 ملی لیئر اسپیسنگ زیادہ تر ایپلی کیشنز کے لیے قابل اطلاق نہیں ہے۔اس وقت، 1mil سے کم انٹر لیئر سپیسنگ کے ساتھ delamination ٹیکنالوجی کو اپنانا ضروری ہے، اور FR4 ڈائی الیکٹرک میٹریل کو ہائی ڈائی الیکٹرک کنسٹنٹ والے مواد سے بدلنا ضروری ہے۔اب، سیرامکس اور برتن والے پلاسٹک 100 سے 300 پی ایس رائز ٹائم سرکٹس کی ڈیزائن کی ضروریات کو پورا کر سکتے ہیں۔

اگرچہ مستقبل میں نئے مواد اور طریقے استعمال کیے جاسکتے ہیں، عام 1 سے 3 این ایس رائز ٹائم سرکٹس، 3 سے 6 ملی لیئر اسپیسنگ، اور FR4 ڈائی الیکٹرک مواد عام طور پر ہائی اینڈ ہارمونکس کو سنبھالنے اور عارضی سگنلز کو کافی کم کرنے کے لیے کافی ہوتے ہیں، یعنی ، عام موڈ EMI بہت کم کم کیا جا سکتا ہے.اس مقالے میں، پی سی بی پرتوں والے اسٹیکنگ کی ڈیزائن مثال دی گئی ہے، اور پرت کا وقفہ 3 سے 6 ملی میٹر سمجھا جاتا ہے۔

برقی مقناطیسی شیلڈنگ

سگنل روٹنگ کے نقطہ نظر سے، ایک اچھی تہہ بندی کی حکمت عملی یہ ہونی چاہیے کہ سگنل کے تمام نشانات کو ایک یا زیادہ تہوں میں رکھا جائے، جو کہ پاور لیئر یا زمینی جہاز کے ساتھ ہیں۔پاور سپلائی کے لیے، ایک اچھی لیئرنگ حکمت عملی یہ ہونی چاہیے کہ پاور لیئر زمینی طیارہ سے متصل ہو، اور پاور لیئر اور گراؤنڈ ہوائی جہاز کے درمیان فاصلہ جتنا ممکن ہو کم ہو، جسے ہم "لیئرنگ" حکمت عملی کہتے ہیں۔

پی سی بی اسٹیک

کس قسم کی اسٹیکنگ حکمت عملی EMI کو بچانے اور دبانے میں مدد کر سکتی ہے؟درج ذیل پرتوں والی اسٹیکنگ اسکیم یہ فرض کرتی ہے کہ بجلی کی فراہمی کا کرنٹ ایک ہی پرت پر بہتا ہے اور ایک ہی پرت کے مختلف حصوں میں ایک وولٹیج یا ایک سے زیادہ وولٹیج تقسیم کیے گئے ہیں۔متعدد پاور پرتوں کے معاملے پر بعد میں بات کی جائے گی۔

4-پلائی پلیٹ

4-پلائی لیمینیٹ کے ڈیزائن میں کچھ ممکنہ مسائل ہیں۔سب سے پہلے، یہاں تک کہ اگر سگنل کی تہہ بیرونی تہہ میں ہے اور پاور اور زمینی طیارہ اندرونی تہہ میں ہے، تب بھی پاور لیئر اور زمینی جہاز کے درمیان فاصلہ بہت زیادہ ہے۔

اگر لاگت کی ضرورت پہلی ہے تو، روایتی 4-پلائی بورڈ کے لیے درج ذیل دو متبادلوں پر غور کیا جا سکتا ہے۔یہ دونوں EMI دبانے کی کارکردگی کو بہتر بنا سکتے ہیں، لیکن یہ صرف اس صورت کے لیے موزوں ہیں جہاں بورڈ پر اجزاء کی کثافت کافی کم ہو اور اجزاء کے ارد گرد کافی جگہ موجود ہو (بجلی کی فراہمی کے لیے مطلوبہ تانبے کی کوٹنگ لگانے کے لیے)۔

پہلی ترجیحی اسکیم ہے۔پی سی بی کی بیرونی پرتیں تمام پرتیں ہیں، اور درمیانی دو پرتیں سگنل/پاور لیئرز ہیں۔سگنل لیئر پر پاور سپلائی کو چوڑی لائنوں کے ساتھ روٹ کیا جاتا ہے، جس سے پاور سپلائی کرنٹ کی راہ میں رکاوٹ اور سگنل مائیکرو اسٹریپ پاتھ کی رکاوٹ کم ہوتی ہے۔EMI کنٹرول کے نقطہ نظر سے، یہ دستیاب بہترین 4-پرت PCB ڈھانچہ ہے۔دوسری سکیم میں، بیرونی پرت طاقت اور زمین کو لے جاتی ہے، اور درمیانی دو تہہ سگنل لے جاتی ہے۔روایتی 4-لیئر بورڈ کے مقابلے میں، اس اسکیم کی بہتری چھوٹی ہے، اور انٹرلیئر مائبادا روایتی 4-لیئر بورڈ کی طرح اچھا نہیں ہے۔

اگر وائرنگ کی رکاوٹ کو کنٹرول کرنا ہے تو، اوپر کی اسٹیکنگ اسکیم کو بجلی کی فراہمی اور گراؤنڈنگ کے تانبے کے جزیرے کے نیچے وائرنگ بچھانے کے لیے بہت محتاط رہنا چاہیے۔اس کے علاوہ، پاور سپلائی یا سٹریٹم پر موجود تانبے کے جزیرے کو DC اور کم فریکوئنسی کے درمیان رابطے کو یقینی بنانے کے لیے زیادہ سے زیادہ ایک دوسرے سے منسلک ہونا چاہیے۔

6-پلائی پلیٹ

اگر 4-پرت بورڈ پر اجزاء کی کثافت بڑی ہے، تو 6-پرت پلیٹ بہتر ہے۔تاہم، 6 لیئر بورڈ کے ڈیزائن میں کچھ اسٹیکنگ اسکیموں کا شیلڈنگ اثر کافی اچھا نہیں ہے، اور پاور بس کا عارضی سگنل کم نہیں ہوتا ہے۔ذیل میں دو مثالیں زیر بحث ہیں۔

پہلی صورت میں، بجلی کی فراہمی اور زمین کو بالترتیب دوسری اور پانچویں تہوں میں رکھا گیا ہے۔تانبے سے پوشیدہ بجلی کی فراہمی کی اعلی رکاوٹ کی وجہ سے، عام موڈ EMI تابکاری کو کنٹرول کرنا بہت ناموافق ہے۔تاہم، سگنل مائبادا کنٹرول کے نقطہ نظر سے، یہ طریقہ بہت درست ہے.

دوسری مثال میں، پاور سپلائی اور گراؤنڈ بالترتیب تیسری اور چوتھی تہوں میں رکھے گئے ہیں۔یہ ڈیزائن بجلی کی فراہمی میں تانبے سے پوشیدہ رکاوٹ کا مسئلہ حل کرتا ہے۔پرت 1 اور پرت 6 کی خراب برقی مقناطیسی شیلڈنگ کارکردگی کی وجہ سے، تفریق موڈ EMI بڑھ جاتا ہے۔اگر دو بیرونی تہوں پر سگنل لائنوں کی تعداد کم سے کم ہے اور لائنوں کی لمبائی بہت کم ہے (سگنل کی سب سے زیادہ ہارمونک طول موج کے 1/20 سے بھی کم)، ڈیزائن ڈیفرینشل موڈ EMI کا مسئلہ حل کر سکتا ہے۔نتائج سے پتہ چلتا ہے کہ تفریق موڈ EMI کا دبانا خاص طور پر اس وقت اچھا ہوتا ہے جب بیرونی تہہ تانبے سے بھری ہو اور تانبے کے پوش علاقے کو گراؤنڈ کیا جاتا ہو (ہر 1/20 طول موج کا وقفہ)۔جیسا کہ اوپر ذکر کیا گیا ہے، تانبا رکھا جائے گا

پوسٹ ٹائم: جولائی 29-2020